引言

钨材料具有抗电子迁移能力强、电阻率低、高温稳定性好、导热及导电性能优良等特性,是集成电路芯片制备过程中一类重要的基础材料。 钨材料主要以薄膜的形式应用在半导体器件中, 被用作高传导性的互连金属、金属层间的通孔、垂直接触的接触孔中的填充物(W plug,钨插塞)以及硅和铝间的隔离层[1-2]。 钨薄膜的制备技术主要包括物理气相沉积(PVD,主要指溅射沉积)和化学气相沉积(CVD)。 由于 CVD 制备薄膜的阶梯覆盖能力强,可以很好地填充通孔, 因此主要应用在接触孔钨插塞的制备工艺中。 与 CVD 工艺相比,PVD 工艺沉积的钨薄膜具有纯度高、致密性好、膜层厚度更均匀、电阻率更低的优势,主要应用于制备集成电路的扩散阻挡层、黏结层和存储器的栅极组件。 PVD 技术具有沉积速率高、污染少、操作过程简便等特点,越来越引起人们的重视。

靶材是 PVD 溅射沉积薄膜的原材料。世界半导体贸易统计协会(World Semiconductor Trade Statistics,WSTS)的统计数据显示[3],2016 年全球溅射靶材市场容量达 113.6 亿美元,预计 2020 年全球溅射靶材市场规模将超过 163 亿美元。 全球靶材应用领域中,虽然半导体行业用溅射靶材的消耗量只占 10 %,但是由于半导体行业对于靶材性能要求的高标准,使得半导体领域用靶材的制备技术难以突破[4]。

随着半导体技术的不断发展, 集成电路中的晶体管和线宽的尺寸越来越小。 芯片制程工艺已经从130nm提升至 7nm,更高端的芯片制程工艺也时有报道。 为了满足现代芯片高精度、小尺寸的需求,对电极和连接器件的布线金属薄膜的性能要求越来越高,这就对溅射靶材的性能提出了更高的要求。本文主要对集成电路用钨溅射靶材的性能要求、 制备技术进行综述,并对钨靶材的发展做出预测。

1、集成电路用钨靶材的性能要求

集成电路芯片制造领域用钨溅射靶材对材料的纯度、致密性、晶粒尺寸及均匀性、织构等方面均具有严格的要求。

1.1纯度

高纯度甚至超高纯度靶材是高端集成电路半导体芯片的必备材料。 钨靶材的纯度决定了钨薄膜的纯度,一般来讲,其纯度需≥99.999 %(5N)[5]。 钨靶材中的杂质会在溅射沉积过程中进入钨薄膜, 薄纯度的降低将导致其电阻率的增加, 同时会造成薄膜均匀性不佳等问题, 最终对器件的良品率造成不利的影响。 Glebovsky[6-7]研究表明,钨靶材中碱金属(Na,K,Li)含量过高,会直接影响钨薄膜的电迁移性能。而且,碱金属离子扩散进入二氧化硅绝缘层会成为可动离子,将增加栅极绝缘材料泄露的风险,降低器件的可靠性, 通常靶材的碱金属含量应控制在0.1×10-6 以内[8]。 此外,氧含量对钨薄膜性能具有至关重要的影响, 氧含量过高容易导致薄膜沉积过程中形成微粒和液滴,造成薄膜缺陷和电路短路,从而引起器件的失效[9];同时,钨薄膜中的氧含量过高也会增加薄膜的电阻率,从而影响信号的传输速率[10]。

集成电路用钨溅射靶材的氧含量应控制在≤100×10-6,针对部分更高端的应用, 靶材中的氧含量应≤20×10-6[11]。 因此,半导体行业的不断发展对靶材提出了越来越高的要求, 需要我们持续降低靶材中杂质元素的含量,提升靶材的纯度。

1.2相对密度

集成电路用溅射靶材的致密性越高越好,一般来讲,半导体行业要求钨靶材的真实密度≥19.15g/cm3,相对密度≥99.5 %[8]。 但是,通过传统粉末冶金工艺制备的钨靶材呈现多孔结构,难以得到相对密度高的板坯。靶材中的孔洞在溅射过程中会产生不均匀冲蚀现象,这是溅射过程中发生微粒现象的主要原因[12]。

薄膜中的微粒越多,器件的良品率越低。 Chi-Fung Lo等[13]研究表明,具有较低相对密度的钨靶材,不仅在溅射时容易形成微粒, 而且会引起薄膜电阻率升高等问题,进而影响钨薄膜的性能,具体来说,钨靶材致密性低会导致溅射的薄膜呈薄片状, 从而增大了薄膜应力,造成晶界取向差,进而增加了薄膜的电阻率。 此外,钨靶材的相对密度越高,薄膜的沉积速率越快,从而提升靶材溅射效率。 因此,获得致密性优良的钨靶材是溅射沉积得到具有低电阻率钨薄膜的重要前提。

1.3晶粒

细晶靶材的溅射沉积速率及成膜均匀性均优于粗晶靶材,因此镀膜设备商通常偏爱细晶靶材。对高纯钨材料(≥99.999%)而言,细晶钨靶材的制备难度极大, 这是因为高纯金属内没有可以阻止晶粒长大的第二相粒子, 同时高纯金属在相变时形核核心数量少,形核率低,导致晶粒难以细化[14]。 因此,集成电路用高纯钨靶材的晶粒度要求通常需≤100 μm。

除晶粒尺寸外,提升靶材中晶粒均匀性同样重要,其直接影响溅射效率和沉积薄膜的均匀性, 而晶粒尺寸的均匀性需从径向和轴向两个维度来进行评价。

因此,减小靶材晶粒尺寸、同时提升晶粒尺寸的均匀性,是靶材制备领域一个重要的研究方向。

1.4织构

钨靶材的织构(多晶体的晶粒取向分布规律)对溅射薄膜的影响往往被人们所忽视, 它对溅射沉积而成的薄膜厚度均匀性具有显著的影响。Takafumi[15]研究表明,用作集成电路栅极材料的钨薄膜,其厚度的差异将影响栅极电阻率的稳定性, 从而影响晶体管的性能,最终降低集成电路的良品率。 目前,溅射得到钨薄膜的厚度变化仅能控制在3%左右, 为了进一步提升芯片的集成度、运行速度和可靠性,对钨薄膜的厚度均匀性提出了更高的要求(≤1 %)[16]。钨靶材是多晶结构, 其溅射沉积得到薄膜厚度的均匀性与靶材单个晶体的取向分布有很大的关系。因此,应保证钨靶材厚度方向上的织构在整个靶材溅射生命周期内的均匀性。此外,为了确保钨靶材织构批次间的稳定性,产品一旦被客户验证通过,其制备工艺随之固定,并且不可轻易更改。

2、集成电路用钨靶材的制备技术

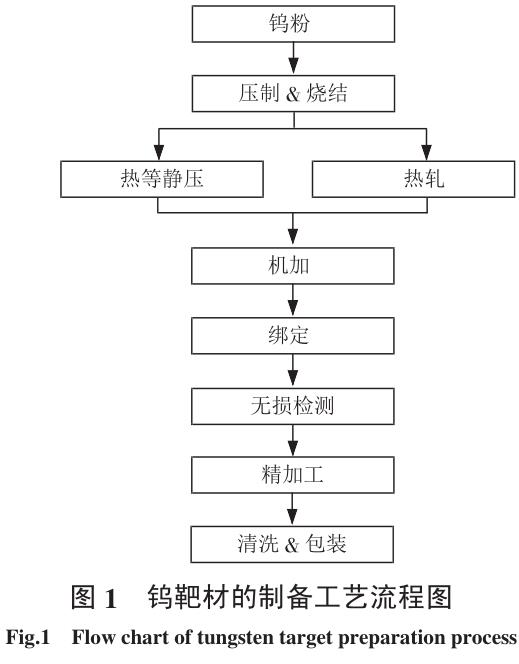

由于钨材料熔点高和脆性大, 钨靶材的整个制备工艺流程主要沿用传统的粉末冶金工艺。 如图 1所示,从钨粉到靶材,需要进行两次致密化处理。 第一次致密化不论是通过冷等静压 (CIP) 还是热压(HP)工艺,其制备得到坯体的致密度均偏低,所以通常需要进行二次致密化来提升其相对密度。目前,最常见的二次致密化工艺是热等静压(HIP)和热轧(Hot Rolling)[17-20]。 得到高致密度的钨板后,需进行切割及表面处理, 然后再和导电及导热性能优良且具有一定强度的背板绑定[21],进而通过超声无损探伤(C-SCAN)进行焊合率的检验(≥95 %),最后通过精密加工,无尘清洗、包装后达到电子级要求,成为合格的靶材产品。

为了制备致密度高、 晶粒均匀且氧含量低的钨板,国内外研究者[22-30]采用不同的热机械处理工艺进行钨板材的制备, 其中主要为以热等静压和热轧为主流的二次致密化工艺, 下面将逐一介绍这两种工艺及其组合。

2.1热等静压(HIP)工艺

热等静压工艺是指在钨靶材致密化工序中引入热等静压技术。 热等静压技术是一种不同于传统无压或者热压致密化的工艺技术,产品在致密化时,被施以各向同等的压力,在高温高压的共同作用下,产品得到致密化,从而得到致密性高、组织结构均匀的靶材产品。

美国 Praxair 公司的 Lo 等[22]采用 HIP 工艺进行钨板的制备。 选用粒径<10 μm 的钨粉,工艺温度1 400 ℃,保温时间 7 h,压力 276 MPa。 选用包套材料的熔点需高于热等静压的工艺温度, 常用的包套材料包括钛、 铁等。 作者采用该工艺得到了氧含量≤300×10-6 且相对密度达 97 %的钨板, 此外,通过细化钨粉的粒径,可进一步提升钨板的相对密度。但是,如果板坯的直径超过厚度 3 倍以上,则需要在HIP 工艺前加入 CIP 工艺,以确保钨板的致密度。

为了进一步提升钨溅射靶材的致密性, 研究者在热等静压之前,先对生坯进行一次致密化,一次致密化工艺主要包括冷等静压、真空常压烧结、热压烧结等,进而再采用热等静压技术对坯体进行二次致密化,这种方法有助于得到相对密度≥99 %的钨靶材。

日本 Nippon Tungsten 公司的 Shibuya 等[23]通过组合 CIP 和 HIP 两种工艺过程, 进行钨靶材的制备。 首先采用 CIP 工艺压制钨粉(粒径 0.5~4 μm),压力≥350 MPa,得到钨生坯;再通过除气和烧结工艺(温度≥1 600 ℃,保温时间≥5 h)得到钨烧结坯(密度 18.8 g/cm3);最后采用 HIP 工艺进行二次致密化,温度≥1 900 ℃,压力≥150 MPa。 最终得到了密度为 19.28 g/cm3 的板坯。 利用这套制备工艺得到的板坯孔隙率低,微观组织均匀,且晶粒具有各向同性的特征,平均晶粒尺寸仅为 15 μm。

日本 Nikko Materials 公司的 Suzuki[24]结合 HP和HIP 工艺,进行高致密钨靶材的制备研究。 首先采用HP 工 艺 制 备 烧 结 坯(温 度1600 ℃ , 压 力≥200 kg/cm2),坯体的相对密度可达 93 %;进而利用 HIP 工艺进行板坯的二次致密化(温度1700 ℃,压力≥1000 kg/cm2), 板坯的相对密度达到 99 %以上,平均晶粒尺寸≤100 μm,氧含量≤20×10-6。

2.2热轧(Hot Rolling)工艺

轧制属于金属变形加工工艺, 而热轧是指在材料的再结晶温度以上进行的轧制。一般来讲,通过常规粉末烧结技术难以获得高致密的钨材料, 热轧技术是一种有效地、 可以进一步提升钨烧结体致密性的方法;此外,通过热轧,可以有效地调控基体的显微结构。

美国 Tosoh 公司的 Ivanov 等[25,30]结合 HP 和热轧工艺, 进行高致密钨靶材的制备研究。 首先采用HP 工艺制备得到相对密度为95%的烧结坯, 再利用热轧工艺进一步提升钨板的致密度。 轧制温度为1 400~1 700 ℃,累计变形量>40 %,最终得到相对密度≥97.5 %的钨板,板坯的平均晶粒尺寸≤100 μm,氧含量≤100×10-6。

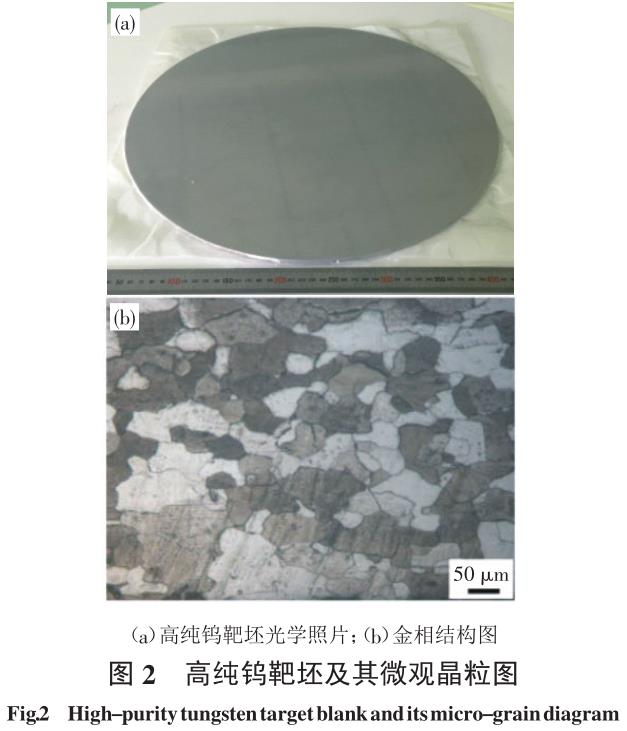

厦门虹鹭钨钼工业有限公司采用粉末冶金和压力加工的工艺路线进行高纯钨靶材的制备。 虹鹭具备生产纯度≥99.999 9 %(6N) 超高纯钨粉的能力,选用超高纯钨粉为原料进行钨靶坯的制备, 得到靶坯的纯度可达 99.999 5 %(5N5)以上,且相对密度≥99.5 %,氧含量<10×10-6,晶粒尺寸≤50 μm(见图 2),钨靶材综合性能达到国外同类产品的水平。

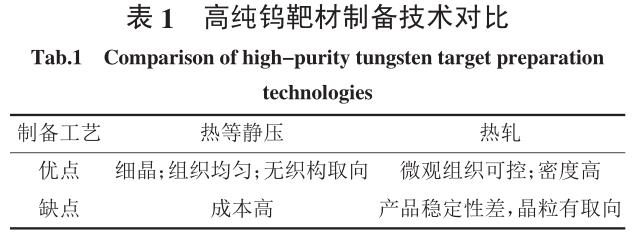

高纯钨靶材制备技术的特点总结如表 1 所示。

采用 HIP 工艺制备钨靶材,可以有效地控制晶粒的大小,有助于得到晶粒细小的钨靶材;该工艺加热过程均匀,有助于获得组织结构均匀的钨靶材,并且晶粒不具有取向性, 因而更容易通过溅射得到一致性好的钨薄膜;此外 HIP 工艺针对脆性大的钨材料有更好的压缩成型的作用;但是,HIP 工艺需要的热等静压炉和高纯包套材料(适用于钨材料)的价格异常昂贵,这成为制约 HIP 工艺在靶材制备方面推广的主要原因。 相对于 HIP 工艺,热轧工艺制备得到的钨靶材具有晶粒大小可控的特性;然而,该工艺步骤多,参数波动因素大,人为操作引起的误差较大,产品质量的一致性不高, 并且轧制容易导致织构的取向性;但从另一方面看,可以通过控制轧制工艺来调整靶材的织构取向,获取具有最优织构取向的靶材,从而达到提升钨靶材溅射性能的目的。

3、未来的发展趋势预测

根据超大规模集成电路(VLSI)技术发展的趋势,芯片制造的要求越来越严格,集成电路的集成度越来越高,特征尺寸越来越小。 PVD 溅射而成钨薄膜的优点(纯度高,致密性好,膜层均匀)正好可以匹配集成电路上栅极和布线材料小而精的发展需求。

但是, 钨靶材溅射制备的薄膜的电阻率达到了钨材料电阻率的 2 倍, 进一步降低钨薄膜的电阻率是芯片制造商提出的重要需求, 也必将会成为一个重要的研究方向。

日本 JX Nippon Mining & Metals 公司的 Ohashi[31]和 Kaminaga[32]对如何降低钨薄膜的电阻率进行了深入的研究, 主要采取的方法是对钨靶材基体中的微量元素进行分析,研究发现,通过控制碳元素和钼元素的含量,可以有效地降低钨薄膜的电阻率。 此外,为了满足溅射薄膜的均匀性和最大程度减少微粒飞溅, 钨靶材的微观组织均匀性是另一个重要的研究方向。 钨晶粒在制备过程中异常长大容易降低板材及其晶界的强度,破坏微观组织均匀性,因此 Suzuki[33-34]和 Ohashi[35]通过调控钨基体中的磷元素和铁元素,可以有效地抑制钨晶粒的异常生长, 从而成功地降低了钨靶材的晶粒尺寸, 最终提升了靶材的溅射效率和钨薄膜的均匀性。

基于以上分析,笔者预计未来钨溅射靶材的发展趋势及目标如下:(1)提升靶材纯度,≥6N;(2)降低靶材氧含量,≤5×10-6;(3)减小靶材晶粒尺寸,同时提高其织构均匀性;(4)降低沉积钨薄膜的电阻率。目前具备规模化生产集成电路用钨靶材的企业数量相对较少,主要分布在美国和日本,产业集中度高。 这些跨国集团产业链完整,具有包括金属提纯、靶材制造、 溅射镀膜和终端应用等各个环节的规模化生产能力, 它们在掌握先进技术以后实施技术垄断和封锁,主导着技术革新和产业发展。高纯钨靶材比较成熟的制备工艺主要包括热等静压及热轧工艺,而一些新技术,如采用化学气相沉积法制备钨靶材,也时有报道,但这些新技术还存在诸如成本高、产品致密度低、 稳定性差、 溅射薄膜电阻率高等不足,阻碍了大规模的商业化应用。

中国钨矿资源储量高居世界第一, 但是制备集成电路用钨溅射靶材的技术水平依然远远落后于世界先进水平, 相关产品严重依赖进口。 随着人工智能、大数据、物联网等高端科技的发展,智能芯片和智能硬件的需求量剧增, 其中海量的数据需要大量的存储设备,所以高端钨溅射靶材的研究、制备和国产化变得越来越重要。因此,加强高纯靶材制备的机

理研究,突破国外核心制备技术壁垒,对于高端靶材的国产化、 提升行业的发展自主性具有十分重要的意义。

参考文献:

[1]SUGURO K,NAKASAKI Y,INOUE T,et al.Reaction kinetics in

tungsten/barrier

metal/silicon

systems

[J].Thin

Solid

Films,

1988,166:1-14.

[2] COLLINS J,NARASIMHAN M K,LIU J,et al.High temperature

tungsten metallization process:US8617985 B2[P].2013-12-31.

[3] WSTS Semiconductor Market Forecast Fall 2019[EB/OL].San Jose,

California,2019,https://www.wsts.org/.

[4] FAN V,HARMAN D,JEWETT J,et al.Evaluation of process for

semiconductor

fabrication

materials

that

are

better

for

the

environment [J].Intel Technology Journal,2008,12:69 -75.DOI:

10.1535/itj.1201.07.

[5]RADIC

N,TONEJC

A,IVKOV

J,et

al.Sputter -deposited

amorphous -like tungsten

[J].Surface & Coatings Technology,

2004,180/181:66-70.

[6]GLEBOVSKY V G,MARKARYANTS E A,TITOV E V.Deposition

of TiW thin films by magnetron co-sputtering[J].Materials Letters,

1994,21(1):89-93.

[7]GLEBOVSKY V G,YASCHAK V Y,BARANOV V V,et al.

Properties of titanium-tungsten thin films obtained by magnetron

sputtering of composite cast targets [J].Thin Solid Films,1995,257

(1):1-6.

[8]YU Y,SONG J,BAI F,et al.Ultra -high purity tungsten and its

applications [J].International Journal of Refractory Metals & Hard

Materials,2015,53(part B):98-103.

[9]WINKLER J,LINKE D C.Sputtering targets:The advantages of

powder metallurgy in the production process [J].Powder Metallurgy

Review,2018:73-87.https://www.pm-review.com/powder-metallurgy

-review -archive/2018 -archive/powder -metallurgy -review -

autumn-2018-vol-7-no-3/.

[10]SARKAR J.Sputtering materials for VLSI and thin film devices[M].

US:Elsevier Inc. Publisher,2013:315.

[11]MAILLE L,SANT C,GARNIER P.A nanometer scale surface

morphology study of W thin films

[J].Materials Science and

Engineering:C,2003,23(6/7/8):913-918.

[12]LO C F,MCDONALD P,DRAPER D,et al.Influence of tungsten

sputtering target density on physical vapor deposition thin film

properties[J].Journal of Electronic Materials,2005,34:1468-1473.

[13]LO C F,DRAPER D,GILMAN P S.Method of making high density

sputtering targets:US6165413[P].2000-12-26.

[14]DUNLOP J A,YUAN J,KARDOKUS K,et al.Sputtering target with

ultra-fine oriented grains and method of making same:US 5809393

A[P].1998-09-15.

[15]TAKAFUMI D,SHINICHIRO S.Tungsten target:WO 2018/179770

[P].2018-10-04.

[16]WATANABE K,YABE Y,ISHIGAMI T,et al.Tungsten sputtering

target and method of manufacturing the target:US7718117 [P].

2010-05-18.

[17]白峰.高纯钨合金靶材制备工艺的研究[D].厦门:厦门大学,

2015.

BAI Feng.The study of preparing of high purity tungsten alloy

targets[D].Xiamen:Xiamen University,2015.

[18]姚力军, 相原俊夫, 大岩一彦, 等. 钨靶材的制作方法:

103567444 A[P]. 2014-02-12.

[19]MATHAUDHU S N,DEROSSET A J,HARTWIGC K T,et al.

Microstructures and recrystallization behavior of severely hot -

deformed tungsten[J].Materials Science and Engineering:A,2009,

503(1/2):28-31.

[20]魏修宇,黄江波,龙坚战,等.一种大尺寸高纯钨靶材及其生产

方法:201310670912.5[P].2013-12-12.

[21]雷继锋. 集成电路制造用溅射靶材绑定技术相关问题研究[J].

金属功能材料,2013,20(1):48-53.

LEI Jifeng.Research on bonding technology of sputtering target for

IC manufacturing [J].Metallic Functional Materials,2013,20(1):

48-53.

[22]LO C F,LEE F,GILMAN P S,et al.Method of making high-density,

high-purity tungsten sputter targets:US 6328927 B1[P].2001-12-

11.

[23]SHIBUYA T,TERAMOTO S,MATSUO S,et al.Tungsten based

sintered compact and method for production thereof:US 2007/

0172378 A1[P]. 2007-07-26.

[24]SUZUKI S,MIYASHITA H.Tungsten target for sputtering and

method for preparing thereof:US 6582535 B1[P].2003-06-24.

[25]IVANOV

E

Y.High

purity

target

manufacturing

methods:

US8506882 B2[P].2013-08-13.

[26]NAKAHATA M.Tungsten target and method for producing same:

US 9388489 B2[P].2016-07-12.

[27]TAKUO I.Method of producing tungsten target for sputtering:JP

2003226964 A[P].2003-08-15.

[28]WATANABE K,YABE Y,ISHIGMI T,et al.Tungsten sputtering

target and method of manufacturing the target:US 2005/0029094

A1[P].2005-02-10.

[29]YI W,ROTHERS S T,SUSAN D,et al.Methods of forming three-

dimensional PVD targets:WO 2006/055513 B1[P].2006-11-02.

[30]IVANOV E Y.High purity target manufacturing methods:WO

2006/001976 A3[P].2006-02-16.

[31]OHASHI K,OKABE T.Tungsten sintered compact sputtering target

and tungsten film formed using same target:US 10047433 B2[P].

2018-08-14.

[32]KAMINAGA K,OHASHI K.Tungsten sintered compact sputtering

target and tungsten film formed using said target:US 2018/0261438

A1[P].2018-09-13.

[33]SUZUKI R,ODA K.Tungsten sintered sputtering target:US2011/

0094879 A1[P].2011-04-28.

[34]SUZUKI R,ODA K.Tungsten sintered sputtering target:US 2016/

014790 A1[P].2016-01-14.

[35]OHASHI K,OKABE K.Tungsten sintered compact sputtering target

and method for producing same:US 9812301 B2[P].2017-11-07.

相关链接